Flip Flops

Flip Flops

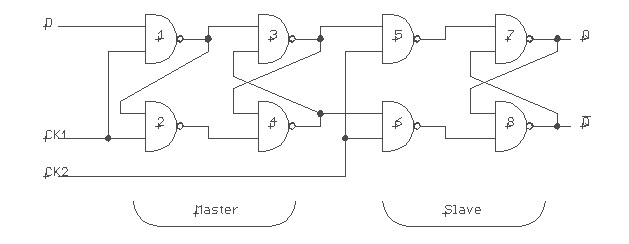

For my registers I use a master-slave D type flip-flop. This looks like :

which I found on Wikipedia.

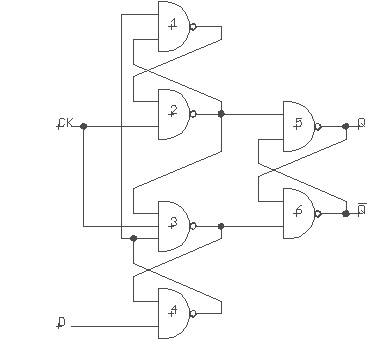

It's usually shown with a single clock input with the second clock being derived as an inverse of the first. I chose to explicitly have two clocks to have better control over timing. The reason why I was (overly) defensive was because I'd first tried using the "classic positive edge clocked D type flip" you can see on the same Wikipedia page. This looks like:

This worked entirely correctly as a flip flop. The problems occurred when I tried having a bunch of them set up to form a shift-register. The results were erratic to say the least. The problem is, I think, the lack of control I have over setup and hold times so it wasn't brilliant for a synchronous system. Some of the flips flops switched before other had got going and so it was all very unhappy. I had half anticipated the problem so I wasn't completely surprised/disappointed. It'd have been nice if it had worked and I thought worth a try.

The big mistake I made was not providing a clock enable control input for my 16 bit registers. This means that if I want a register to keep a value from one clock cycle to the next I have to feed its value back to the input. Which not only means I need wider multiplexers on the inputs but I also have to tee the output and send it back round to the input multiplexer which adds a lot of unhelpful clutter. This is just a stupid mistake. I may have been nervous about the implications for hold times when I was thinking of using the edge triggered flip flop at the start but once I switched to the master-slave flip flop I should definitely have added the clock enable. I guess just another example of not noticing when early assumptions are negated by later developments.

|

|

© 2014-2016 James Newman.